# KS57C0002/0004 4-BIT CMOS Microcontroller

# **Product Specification**

### **OVERVIEW**

The KS57C0002/0004 single-chip CMOS microcontroller is designed for high-performance using Samsung's newest 4-bit CPU core. With a four-channel comparator, eight LED direct drive pins, serial I/O interface, and a versatile

8-bit timer/countkxcellent design solution for a variety of general-purpose applications.

Up to 24 pins of the 30-pin SDIP package can be dedicated to I/O. Five vectored interrupts provide fast response to internal and external events. In addition, the KS57C0002/0004's advanced CMOS technology ensures low power consumption and a wide operating voltage range.

#### **FEATURES**

# Memory

- 256 × 4-bit data memory (KS57C0002)

512 × 4-bit data memory (KS57C0004)

- 2048 × 8-bit program memory (KS57C0002)

4096 × 8-bit program memory (KS57C0004)

# **24 I/O Pins**

- I/O: 18 pins, including 8 highcurrent pins

- Input only: 6 pins

### Comparator

- 4-channel mode with internal reference (4-bit resolution) and 16-step variable reference voltage

- 3-channel mode with external reference

- 150 mV resolution (minimum)

## **8-Bit Basic Timer**

Programmable interval timer

# 8-Bit Timer/Counter

- Programmable interval timer

- External event counter function

- Timer/counter clock output to TCLO0 pin

#### **Watch Timer**

- Interval generation: 0.5 s, 3.9ms at 32768 Hz

- Four frequency outputs to the BUZ pin

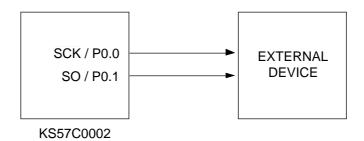

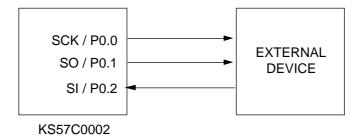

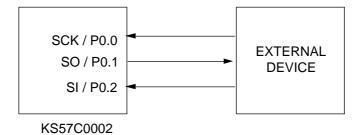

#### 8-Bit Serial I/O Interface

- 8-bit transmit/receive mode

- 8-bit receive-only mode

- LSB-first or MSB-first transmission selectable

- Internal or external clock source

# **Bit Sequential Carrier**

Support for 16-bit serial data transfer in arbitrary format

# Interrupts

- Two external interrupt vectors

- Three internal interrupt vectors

- Two quasi-interrupts

# **Memory-Mapped I/O Structure**

Data memory bank 15

#### **Power-Down Modes**

Idle mode (only CPU clock stops)

Stop mode (system clock stops)

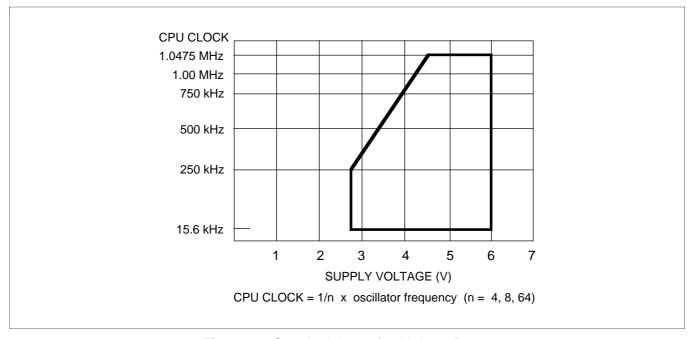

#### **Oscillation Sources**

- Crystal, ceramic, or RC for system clock (RC is only for the KS57C0002)

- Crystal, ceramic: 4.19 MHz (typical)

- RC: 1 MHz

- CPU clock divider circuit (by 4, 8, or 64)

# **Instruction Execution Times**

• 0.95, 1.91, 15.3 μs at 4.19 MHz

# **Operating Temperature**

– 40 °C to 85 °C

### **Operating Voltage Range**

2.7 V to 6.0 V

### Package Type

30 SDIP, 32 SOP

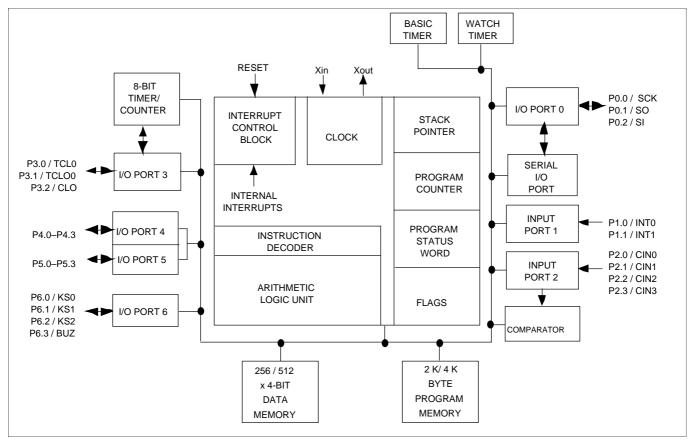

Figure 1. KS57C0002/0004 Block Diagram

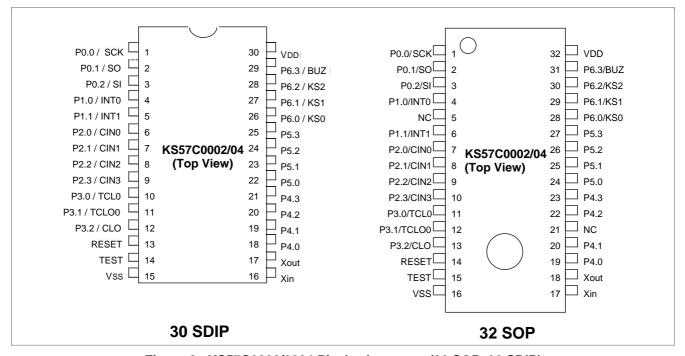

Figure 2. KS57C0002/0004 Pin Assignments (32 SOP, 30 SDIP)

Table 1. KS57C0002/0004 Pin Descriptions

| Pin Name                           | Pin Type | Description                                                                                                                                                                                                                       | Number               | Share Pin                |

|------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------------|

| P0.0<br>P0.1<br>P0.2               | I/O      | 3-bit I/O port. 1-bit or 3-bit read/write and test is possible. Pull-up resistors are assignable to input pins by software and are automatically disabled for output pins. Pins are individually configurable as input or output. | 1<br>2<br>3          | SCK<br>SO<br>SI          |

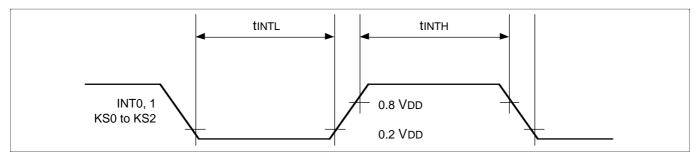

| P1.0<br>P1.1                       | I        | 2-bit input port. 1-bit or 2-bit read and test is possible. Pull-up resistors are assignable by software.                                                                                                                         | 4<br>5               | INT0<br>INT1             |

| P2.0-P2.3                          | l        | 4-bit input port. 1-bit or 4-bit read and test is possible.                                                                                                                                                                       | 6–9                  | CIN0-CIN3                |

| P3.0<br>P3.1<br>P3.2               | I/O      | Same as port 0                                                                                                                                                                                                                    | 10<br>11<br>12       | TCL0<br>TCLO0<br>CLO     |

| P4.0–P4.3<br>P5.0–P5.3             | I/O      | 4-bit I/O ports. 1-, 4-, or 8-bit read/write and test is possible. Pins are individually configurable as input or output. Ports can be configurable as n-channel open-drain by mask option (maximum 9V).                          | 18–21<br>22–25       | _                        |

| P6.0<br>P6.1<br>P6.2<br>P6.3       | I/O      | 4-bit I/O port. 1-bit or 4-bit read/write and test is possible. Pull-up resistors are assignable to input pins by software and are automatically disabled for output pins. Pins individually configurable as input or output.     | 26<br>27<br>28<br>29 | KS0<br>KS1<br>KS2<br>BUZ |

| INT0                               | I        | External interrupts with rising/falling edge detection                                                                                                                                                                            | 4                    | P1.0                     |

| INT1                               | I        | External interrupts with rising/falling edge detection                                                                                                                                                                            | 5                    | P1.1                     |

| CIN0-CIN3                          | I        | 4-channel comparator input. CIN0–CIN2: comparator input only. CIN3: comparator input or external reference input                                                                                                                  | 6–9                  | P2.0-P2.3                |

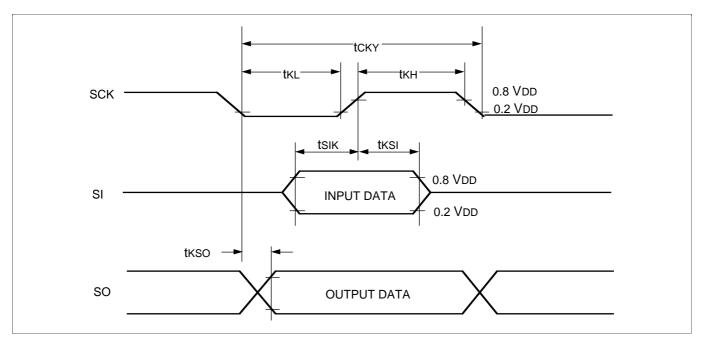

| SCK                                | I/O      | Serial interface clock signal                                                                                                                                                                                                     | 1                    | P0.0                     |

| SO                                 | I/O      | Serial data output                                                                                                                                                                                                                | 2                    | P0.1                     |

| SI                                 | I/O      | Serial data input                                                                                                                                                                                                                 | 3                    | P0.2                     |

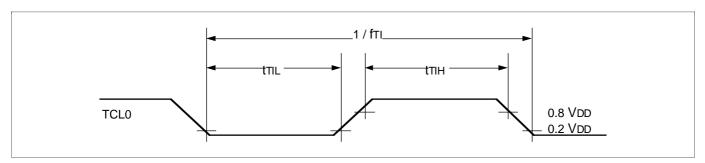

| TCL0                               | I/O      | External clock input for timer/counter                                                                                                                                                                                            | 10                   | P3.0                     |

| TCLO0                              | I/O      | Timer/counter clock output                                                                                                                                                                                                        | 11                   | P3.1                     |

| CLO                                | I/O      | CPU clock output                                                                                                                                                                                                                  | 12                   | P3.2                     |

| BUZ                                | I/O      | 2 kHz, 4 kHz, 8 kHz, or 16 kHz frequency output at 4.19 MHz for buzzer sound                                                                                                                                                      | 29                   | P6.3                     |

| KS0-KS2                            | I/O      | Quasi-interrupt input with falling edge detection                                                                                                                                                                                 | 26–28                | P6.0-P6.2                |

| $V_{DD}$                           | _        | Main power supply                                                                                                                                                                                                                 | 30                   | _                        |

| V <sub>SS</sub>                    | _        | Ground                                                                                                                                                                                                                            | 15                   | _                        |

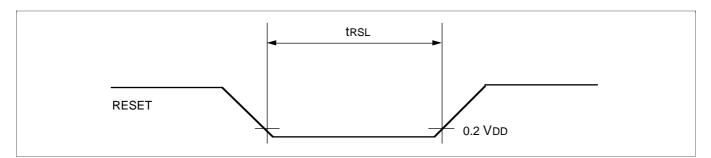

| RESET                              | I        | Reset signal                                                                                                                                                                                                                      | 13                   | _                        |

| TEST                               | I        | Test signal input (must be connected to V <sub>SS</sub> )                                                                                                                                                                         | 14                   | _                        |

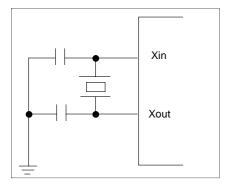

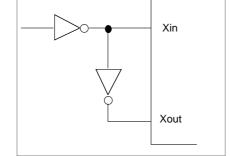

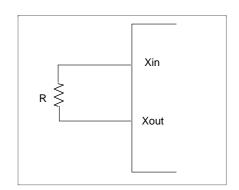

| X <sub>in</sub> , X <sub>out</sub> | _        | Crystal, ceramic, or RC oscillator signal for system clock                                                                                                                                                                        | 16, 17               | _                        |

Table 2. Supplemental KS57C0002/0004 Pin Data

| Pin Numbers | Pin Names       | Share Pins            | I/O Type | Reset Value | Circuit Type |

|-------------|-----------------|-----------------------|----------|-------------|--------------|

| 1, 2, 3     | P0.0-P0.2       | SCK, SO, SI           | I/O      | Input       | 5            |

| 4, 5        | P1.0, P1.1      | INTO, INT1            | I        | Input       | 3            |

| 6–9         | P2.0-P2.3       | CIN0-CIN3             | I        | Input       | 6, 8 *       |

| 10–12       | P3.0-P3.2       | TCL0, TCLO0, CLO      | I/O      | Input       | 5            |

| 13          | RESET           | _                     | I        | _           | 9            |

| 14          | TEST            | _                     | I        | _           |              |

| 15          | V <sub>SS</sub> | _                     | _        | _           |              |

| 16, 17      | Xin, Xout       | _                     | _        | _           | _            |

| 18–21       | P4.0-P4.3       | _                     | I/O      | Input       | 7            |

| 22–25       | P5.0-P5.3       | _                     | I/O      | Input       | 7            |

| 26–29       | P6.0-P6.3       | KS0, KS1, KS2,<br>BUZ | I/O      | Input       | 5            |

| 30          | $V_{DD}$        | _                     | _        | _           |              |

<sup>\*</sup> I/O circuit type 8 is for P2.3 only.

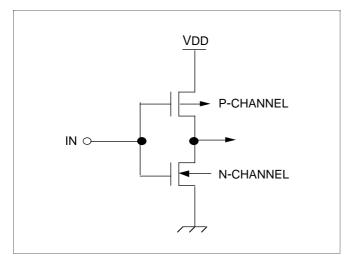

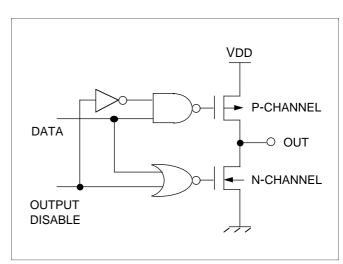

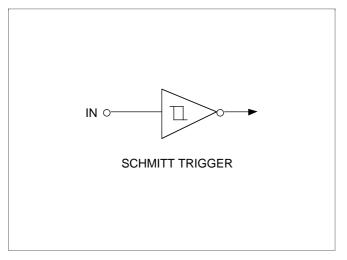

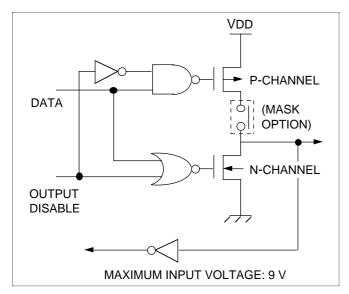

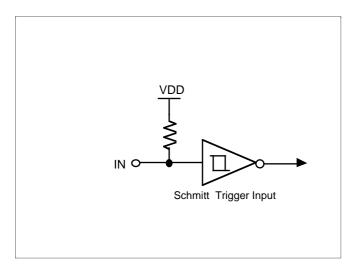

Figure 3. Pin Circuit Type 1

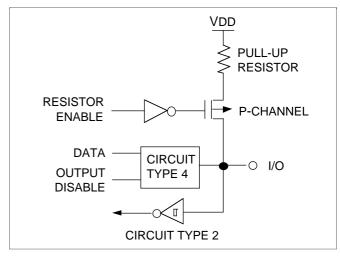

Figure 6. Pin Circuit Type 4

Figure 4. Pin Circuit Type 2

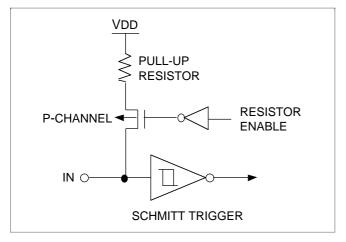

Figure 7. Pin Circuit Type 5

Figure 5. Pin Circuit Type 3

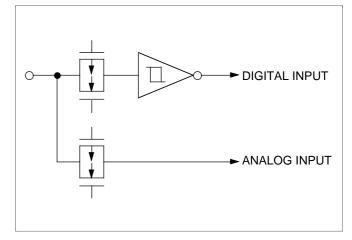

Figure 8. Pin Circuit Type 6

DIGITAL INPUT

ANALOG INPUT

EXTERNAL VREF

Figure 9. Pin Circuit Type 7

Figure 10. Pin Circuit Type 8

Figure 11. Pin Circuit Type 9

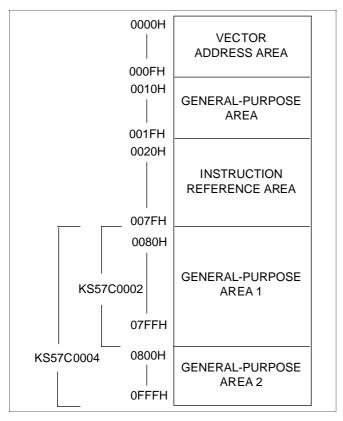

16-byte general-purpose area16-byte area for vector addresses

general-purpose area

96-byte instruction reference area

— 1920-byte (KS57C0002), 3968-byte (KS57C0004)

# PROGRAM MEMORY (ROM)

ROM maps for KS57C0002/0004 devices are mask programmable at the factory. In their standard configuration, the device's  $2048 \times 8$ -bit (KS57C0002), or  $4096 \times 8$ -bit (KS57C0004) program memory has four areas that are directly addressable by the program counter ( PC):

Figure 12. ROM Map

# 7 6 5 4 3 2 1 0 0000H RESET **INTB** 0002H INT<sub>0</sub> 0004H 0006H INT1 INTS 0008H 000AH INTT0

Figure 13. Vector Address Map

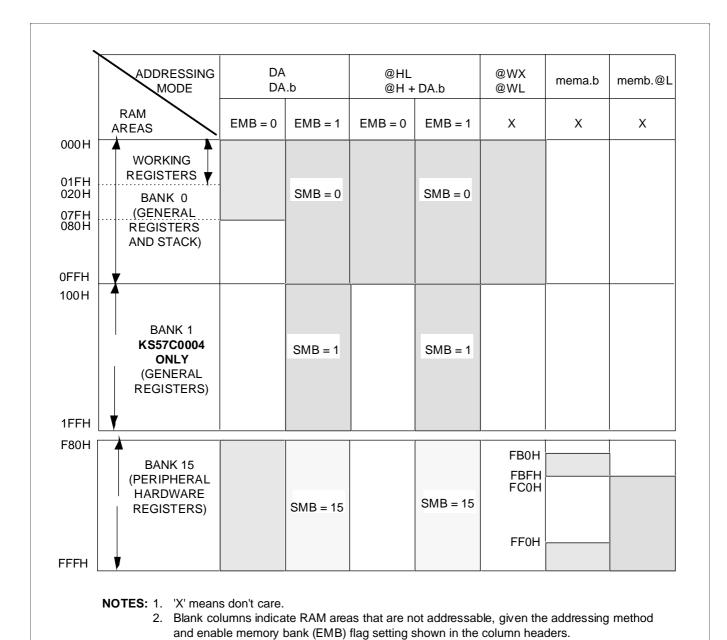

# **DATA MEMORY (RAM)**

In its standard configuration, the 256× 4 -bit (KS57C0002), or the 512 ×4-bit (KS57C0004) data memory has four areas:

- 32 ×4-bit working registers

- 224× 4-bit general-purpose area in bank0 which is also used as the stack area

- 256×4 -bit general-purpose area in bank1 (KS57C0004 only)

- 128× 4-bit area in bank 15 for memory-mapped I/O addresses

# I/O MAP FOR HARDWARE REGISTERS

Table 3 contains detailed information about I/O mapping for peripheral hardware in bank 15 (register locations F80H–FFFH).

Figure 14. Data Memory (RAM) Address Structure

Table 3. I/O Map for Memory Bank 15

|           | Memory Bank 15 |                      |                                    |             |          |     |       | sing Mode | <b>:</b> |

|-----------|----------------|----------------------|------------------------------------|-------------|----------|-----|-------|-----------|----------|

| Address   | Register       |                      | Name                               |             |          | R/W | 1-Bit | 4-Bit     | 8-Bit    |

| F81H-F80H | SP             |                      | Stack                              | Pointer     |          | R/W | No    | No        | Yes      |

| F85H      | BMOD           | Bas                  | Basic Timer Mode Register          |             |          | W   | .3    | Yes       | No       |

| F87H-F86H | BCNT           | Basic                | Timer C                            | ounter Re   | gister   | R   | No    | No        | Yes      |

| F89H-F88H | WMOD           | Wat                  | ch Timer                           | Mode Re     | gister   | W   | No    | No        | Yes      |

| F91H-F90H | TMOD0          | Timer                | /Counter                           | 0 Mode R    | egister  | W   | .3    | No        | Yes      |

| F95H-F94H | TCNT0          | Timer/C              | Counter 0                          | Counter I   | Register | R   | No    | No        | Yes      |

| F97H-F96H | TREF0          | Timer                | Counter (                          | ) Referen   | ce Reg   | W   | No    | No        | Yes      |

| FB0H      | PSW            | IS1                  | IS0                                | EMB         | ERB      | R/W | Yes   | Yes       | Yes      |

| FB1H      | -              | C (2)                | SC2                                | SC1         | SC0      | R   | No    | No        |          |

| FB2H      | IPR            |                      | SIO Mode                           | e Registe   | r        | W   | IME   | Yes       | No       |

| FB3H      | PCON           | Po                   | ower Con                           | trol Regis  | ter      | W   | No    | Yes       | No       |

| FB4H      | IMOD0          | Externa              | ıl Interrup                        | t 0 Mode    | Register | W   | No    | Yes       | No       |

| FB5H      | IMOD1          | Externa              | External Interrupt 1 Mode Register |             |          |     | No    | Yes       | No       |

| FB6H      | IMODK          | Extern               | al Key Int                         | errupt Mo   | de Reg   | W   | No    | Yes       | No       |

| FB8H      |                | "0"                  | "0"                                | IEB         | IRQB     | R/W | Yes   | Yes       | No       |

| FBAH      |                | "0"                  | "0"                                | IEW         | IRQW     | R/W | Yes   | Yes       | No       |

| FBCH      |                | "0"                  | "0"                                | IET0        | IRQT0    | R/W | Yes   | Yes       | No       |

| FBDH      |                | "0"                  | "0"                                | IES         | IRQS     |     |       |           |          |

| FBEH      |                | IE1                  | IRQ1                               | IE0         | IRQ0     |     |       |           |          |

| FBFH      |                | "0"                  | "0"                                | IEK         | IRQK     |     |       |           |          |

| FC0H      | BSC0           | Bi                   | it Sequen                          | tial Carrie | r 0      | R/W | Yes   | Yes       | Yes      |

| FC1H      | BSC1           | Bi                   | it Sequen                          | tial Carrie | r 1      |     |       |           |          |

| FC2H      | BSC2           | Bi                   | it Sequen                          | tial Carrie | r 2      |     |       |           |          |

| FC3H      | BSC3           | Bi                   | it Sequen                          | tial Carrie | r 3      |     |       |           |          |

| FD0H      | CLMOD          | (                    | Clock Mod                          | de Registe  | er       | W   | No    | Yes       | No       |

| FD4H      | CMPREG         | Com                  | parison F                          | Result Re   | gister   | R   | No    | Yes       | No       |

| FD7H-FD6H | CMOD           | Con                  | nparator N                         | Mode Reg    | ister    | R/W | No    | No        | Yes      |

| FDDH-FDCH | PUMOD          | Р                    | ull-up Mo                          | de Regist   | er       | W   | No    | No        | Yes      |

| FE1H-FE0H | SMOD           | SIO Mode Register    |                                    |             | W        | .3  | No    | Yes       |          |

| FE2H      | P2MOD          | Port 2 Mode Register |                                    |             | W        | No  | Yes   | No        |          |

| FE5H-FE4H | SBUF           |                      | SIO Buffer Register                |             |          | R/W | No    | No        | Yes      |

| FE9H-FE8H | PMG1           |                      | Port Mod                           | e Group 1   |          | W   | No    | No        | Yes      |

| FEBH-FEAH | PMG2           |                      | Port Mod                           | e Group 2   | 2        |     |       |           |          |

2-9

September 1996

Table 3. I/O Map for Memory Bank 15 (Concluded)

|           | Memor    | y Bank 15         | Addressing Mode |       |       |       |  |

|-----------|----------|-------------------|-----------------|-------|-------|-------|--|

| Address   | Register | Name              | R/W             | 1-Bit | 4-Bit | 8-Bit |  |

| FEDH-FECH | PMG3     | Port Mode Group 3 | W               | No    | No    | Yes   |  |

| FF0H      | P0       | Port 0            | R/W             | Yes   | Yes   | No    |  |

| FF1H      | P1       | Port 1            | R               |       |       | No    |  |

| FF2H      | P2       | Port 2            | R               |       |       | No    |  |

| FF3H      | P3       | Port 3            | R/W             |       |       | No    |  |

| FF4H      | P4       | Port 4            | R/W             |       |       | Yes   |  |

| FF5H      | P5       | Port 5            | R/W             |       |       |       |  |

| FF6H      | P6       | Port 6            | R/W             |       |       | No    |  |

# NOTES:

- Bit 0 in the WMOD register must be set to "0".

The carry flag can be read or written by specific bit manipulation instructions only.

# **BIT SEQUENTIAL CARRIER (BSC)**

The bit sequential carrier (BSC) is a 16-bit general register that is mapped in data memory bank 15. Using the BSC, you can specify sequential addresses and bit locations using 1-bit indirect addressing (memb.@L).

BSC bit addressing is independent of the current EMB value. In this way, programs can process 16-bit data by moving the bit location sequentially and then

incrementing or decrementing the value of the L register.

For 8-bit manipulations, the 4-bit register names BSC0 and BSC2 must be specified and the upper and lower 8 bits manipulated separately. If the values of the L register are 0H at BSC0.@L, the address and bit location assignment is FC0H.0. If the L register content is FH at BSC0.@L, the address and bit location assignment is FC3H.3.

**Table 4. BSC Register Organization**

| Name | Address | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|------|---------|--------|--------|--------|--------|

| BSC0 | FC0H    | BSC0.3 | BSC0.2 | BSC0.1 | BSC0.0 |

| BSC1 | FC1H    | BSC1.3 | BSC1.2 | BSC1.1 | BSC1.0 |

| BSC2 | FC2H    | BSC2.3 | BSC2.2 | BSC2.1 | BSC2.0 |

| BSC3 | FC3H    | BSC3.3 | BSC3.2 | BSC3.1 | BSC3.0 |

# PROGRAMMING TIP — Using the BSC Register to Output 16-Bit Data

To use the bit sequential carrier (BSC) register to output 16-bit data (5937H) to the P3.0 pin:

**BITS EMB SMB** 15 EA,#37H LD LD BSC0,EA  $BSC0 \leftarrow A, BSC1 \leftarrow E$ EA,#59H LD LD  $BSC2 \leftarrow A, BSC3 \leftarrow E$ BSC2,EA **SMB** L,#0H LD C,BSC0.@L AGN LDB P3.0 ← C **LDB** P3.0,C **INCS** JR **AGN RET**

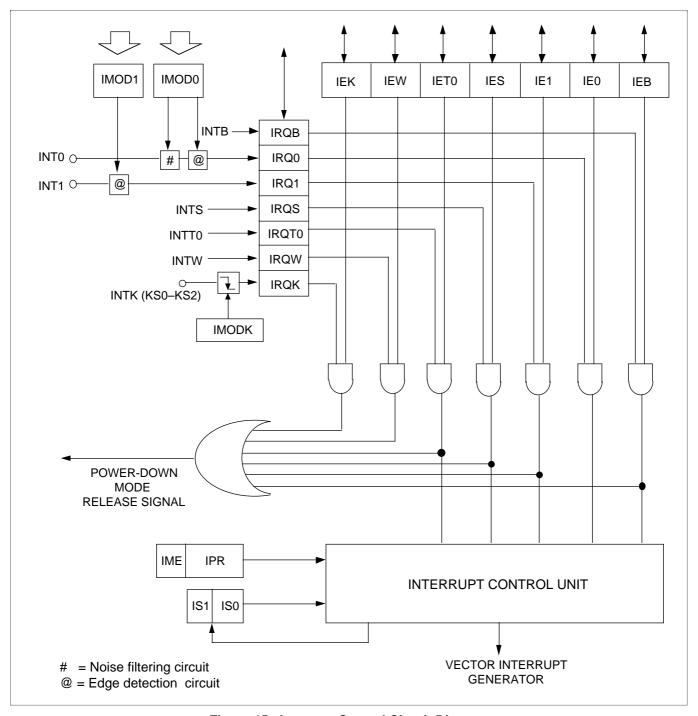

# **INTERRUPTS**

The KS57C0002/0004 microcontroller has two external interrupts, three internal interrupts, and two quasi-interrupts. Table 5 shows the conditions for each interrupt generation. The request flags that actually generate these interrupts are cleared by hardware when the service routine is vectored. However, the quasi-interrupt's request flags must be cleared by software.

Figure 15. Interrupt Control Circuit Diagram

September 1996 2–12

Table 5. Interrupt Request Flag Conditions and Priorities

| Interrupt<br>Source | Internal /<br>External | Condition for IRQx Flag Setting                                             | Interrupt<br>Priority | Request Flag<br>Name |

|---------------------|------------------------|-----------------------------------------------------------------------------|-----------------------|----------------------|

| INTB                | I                      | Reference time interval signal from basic timer                             | 1                     | IRQB                 |

| INT0                | E                      | Rising or falling edge detected at INT0 pin                                 | 2                     | IRQ0                 |

| INT1                | E                      | Rising or falling edge detected at INT1 pin                                 | 3                     | IRQ1                 |

| INTS                | I                      | Completion signal for serial transmit-and-receive or receive-only operation | 4                     | IRQS                 |

| INTT0               | I                      | Signals for TCNT0 and TREF0 registers match                                 | 5                     | IRQT0                |

| INTK *              | E                      | Falling edge is detected at any of the KS0–KS2 pins                         | _                     | IRQK                 |

| INTW *              | I                      | Time interval of 0.5 s or 3.19 ms                                           | _                     | IRQW                 |

<sup>\*</sup> The INTK and INTW are quasi-interrupts and INTK are used only for testing incoming signals.

# **INTERRUPT ENABLE FLAGS (IEx)**

IEx flags, when set to "1", enable specific interrupt requests to be serviced. When the interrupt request flag is set to "1", an interrupt will not be serviced until its corresponding IEx flag is also enabled. The IPR register contains a global disable bit, IME, which disables all interrupt at once.

Table 6. Interrupt Enable and Request Flag

| Address | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------|-------|-------|-------|

| FB8H    | 0     | 0     | IEB   | IRQB  |

| FBAH    | 0     | 0     | IEW   | IRQW  |

| FBBH    | 0     | 0     | 0     | 0     |

| FBCH    | 0     | 0     | IET0  | IRQT0 |

| FBDH    | 0     | 0     | IES   | IRQS  |

| FBEH    | IE1   | IRQ1  | IE0   | IRQ0  |

| FBFH    | 0     | 0     | IEK   | IRQK  |

#### NOTES:

- 1. IEx refers to all interrupt enable flags.

- 2. IRQx refers to all interrupt request flags.

- 3. IEx = "0" is interrupt disable mode.

- 4. IEx = "1" is interrupt enable mode.

#### INTERRUPT PRIORITY

Each interrupt source can also be individually programmed to high levels by modifying the IPR register. When IS1 = 0 and IS0 = 1, a low-priority interrupt can itself be interrupted by a high-priority interrupt, but not by another low-priority interrupt.

If you clear the interrupt status flags (IS1 and IS0) to "0" in a interrupt service routine, a high-priority interrupt can be interrupted by low-priority interrupt (multi-level interrupt). Before the IPR can be modified by 4-bit write instructions, all interrupts must first be disabled by a DI instruction.

When all interrupts are low priority (the lower three bits of the IPR register are "0"), the interrupt requested first will have high priority. Therefore, the first-requested interrupt cannot be superseded by any other interrupt.

If two or more interrupt requests are received simultaneously, the priority level is determined according to the standard interrupt priorities, where the default priority is assigned by hardware when the lower three IPR bits = "0".

2–13 September 1996

In this case, the higher-priority interrupt request is serviced and the other interrupt is inhibited. Then, when the high-priority interrupt is returned from its service routine by an IRET instruction, the inhibited service routine is started.

**Table 7. Interrupt Priority Register Settings**

| IPR.2 | IPR.1 | IPR.0 | Result of IPR Bit Setting                       |

|-------|-------|-------|-------------------------------------------------|

| 0     | 0     | 0     | Process all interrupt requests at low priority. |

| 0     | 0     | 1     | INTB                                            |

| 0     | 1     | 0     | INT0                                            |

| 0     | 1     | 1     | INT1                                            |

| 1     | 0     | 0     | INTS                                            |

| 1     | 0     | 1     | INTT0                                           |

**Table 8. Default Priorities**

0

0

| Source | Default Priority |

|--------|------------------|

| INTB   | 1                |

| INT0   | 2                |

| INT1   | 3                |

| INTS   | 4                |

| INTT0  | 5                |

#### **EXTERNAL INTERRUPTS**

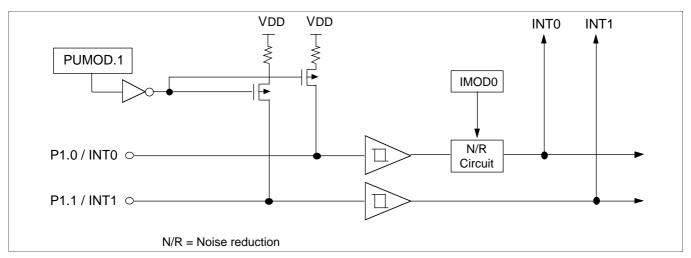

The external interrupt mode registers (IMOD0 and IMOD1) are used to control the triggering edge of the input signal at the INT0 and INT1 pins, respectively.

When a sampling clock rate of fx/64 is used for INT0, an interrupt request flag must be cleared before 16 machine cycles have elapsed. Since the INT0 pin has a clock-driven noise filtering circuit built into it, please take the following precautions when you use it:

- To trigger an interrupt, the input signal width at INTO must be at least two times wider than the pulse width of the clock selected by IMODO. This is true even when the INTO pin is used for general-purpose input.

- Since the INT0 input sampling clock does not operate during Stop or Idle mode, you cannot use INT0 to release power-down mode.

When modifying the IMOD0 and IMOD1 registers, it is possible to accidentally set an interrupt request flag.

To avoid unwanted interrupts, take these precautions when writing your programs:

- 1. Disable all interrupts with a DI instruction.

- 2. Modify the IMOD0 or IMOD1 register.

- 3. Clear all relevant interrupt request flags.

- 4. Enable the interrupt by setting the appropriate IEx flag.

- 5. Enable all interrupts with an El instructions.

Table 9. IMOD0 and IMOD1 Register Organization (4-Bit W)

| IMOD0.3 | 0 | IMOD0.1 | IMOD0.0 | Effect of IMOD0 Settings               |

|---------|---|---------|---------|----------------------------------------|

| 0       |   |         |         | Select CPU clock for sampling          |

| 1       |   |         |         | Select fx/64 sampling clock            |

|         | 0 | 0       | 0       | Rising edge detection                  |

|         | 0 | 0       | 1       | Falling edge detection                 |

|         | 0 | 1       | 0       | Both rising and falling edge detection |

|         | 0 | 1       | 1       | IRQ0 flag cannot be set to "1"         |

| 0       | 0 | 0       | IMOD1.0 | Effect of IMOD1 Settings               |

| 0       | 0 | 0       | 0       | Rising edge detection                  |

|         |   |         | -       |                                        |

Falling edge detection

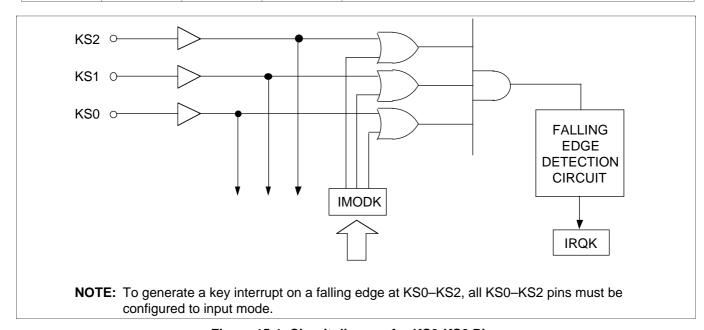

# **EXTERNAL KEY INTERRUPT MODE REGISTER**

The external key interrupt (INTK) mode register, IMODK, is used to select KS pins as interrupt input pins. When a falling edge is detected at one of the KS0–KS2 pins, the IRQK flag is set to "1". This generates an interrupt request and a release signal for power-down mode. To generate a key interrupt on a falling signal edge at KS0–KS2, all of the KS0–KS2 pins must be configured to input mode.

If one or more of the pins which are configured as key Interrupt (KS0–KS2) are in Low input or Low output state, the key Interrupt can not be occurred.

Table 10. IMODK Register Bit Settings (4-Bit W)

| 0 | IMODK.2 | IMODK.1 | IMODK.0 | Effect of IMODK Settings        |

|---|---------|---------|---------|---------------------------------|

| 0 | 0       | 0       | 0       | Disable key interrupt           |

| 0 | 0       | 0       | 1       | Select falling edge at KS0      |

| 0 | 0       | 1       | 0       | Select falling edge at KS1      |

| 0 | 0       | 1       | 1       | Select falling edge at KS0–KS1  |

| 0 | 1       | 0       | 0       | Select falling edge at KS2      |

| 0 | 1       | 0       | 1       | Select falling edge at KS0, KS2 |

| 0 | 1       | 1       | 0       | Select falling edge at KS1–KS2  |

| 0 | 1       | 1       | 1       | Select falling edge at KS0–KS2  |

Figure 15-1. Circuit diagram for KS0-KS2 Pins

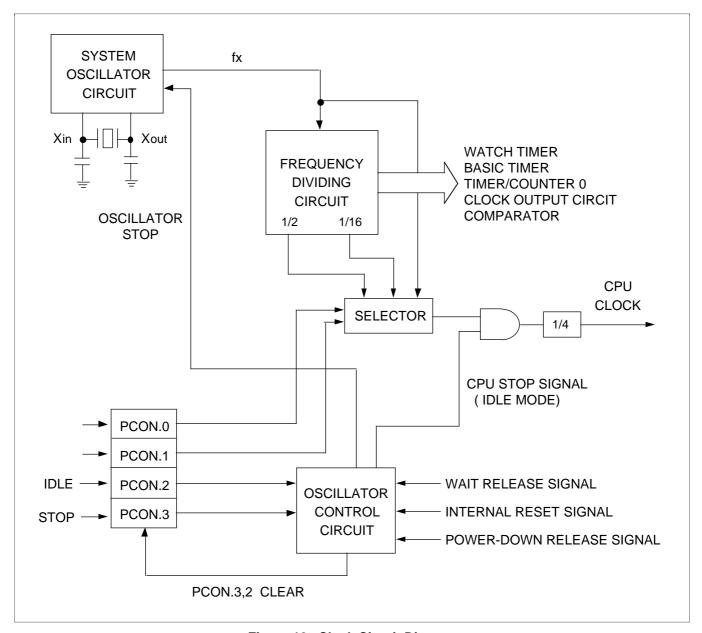

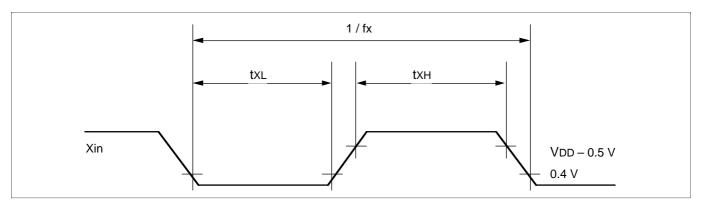

# **OSCILLATOR CIRCUITS**

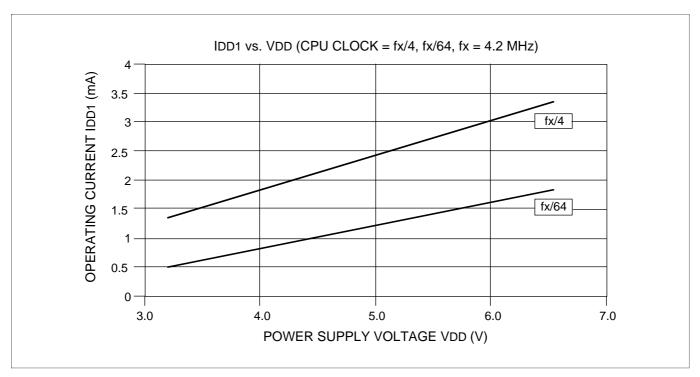

The KS57C0002/0004 system clock circuit is shown in Figure 16 below. By manipulating bits 1 and 0 of the PCON register, the system clock frequency can be divided by 4, 8, or 64.

Figure 16. Clock Circuit Diagram

September 1996 2–16

Figure 17. Crystal/Ceramic Oscillator

Figure 18. External Clock

Figure 19. RC Oscillator (only for the KS57C0002)

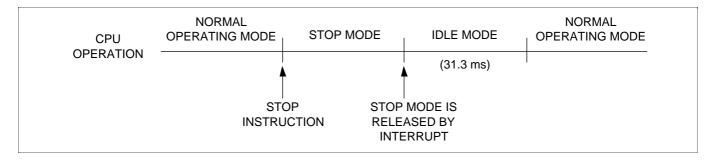

# **POWER CONTROL REGISTER (PCON)**

The power control register, PCON, is used to select the CPU clock frequency and to control CPU operating and power-down modes. PCON bits 3 and 2 are controlled by the STOP and IDLE instructions, which engage the Stop and Idle power-down modes, respectively. Using these instructions, you can initiate a power-down mode at any time, regardless of the current value of the enable memory bank flag (EMB).

Table 11. Power Control Register (PCON) Organization (4-Bit W)

| PCON Bi | t Settings | Resulting CPU Operating Mode |

|---------|------------|------------------------------|

| PCON.3  | PCON.2     |                              |

| 0       | 0          | Normal CPU operating mode    |

| 0       | 1          | Idle power-down mode         |

| 1       | 0          | Stop power-down mode         |

| PCON Bit Settings |        | Resulting CPU Clock Frequency |

|-------------------|--------|-------------------------------|

| PCON.1            | PCON.0 |                               |

| 0                 | 0      | fx/64                         |

| 1                 | 0      | fx/8                          |

| 1                 | 1      | fx/4                          |

# PROGRAMMING TIP — Setting the CPU Clock

To set the CPU clock to 0.95  $\mu s$  at 4.19 MHz:

BITS EMB SMB 15 LD A,#3H LD PCON,A

# **INSTRUCTION CYCLE TIMES**

The unit of time that equals one machine cycle varies depending on how the oscillator clock signal is divided.

Table 12. Instruction Cycle Times for CPU Clock Rates

| Selected<br>CPU Clock | Resulting Frequency | Oscillation<br>Source | Cycle Time (μs) |

|-----------------------|---------------------|-----------------------|-----------------|

| fx/64                 | 65.5 kHz            |                       | 15.3            |

| fx/8                  | 524.0 kHz           | fx = 4.19  MHz        | 1.91            |

| fx/4                  | 1.05 MHz            |                       | 0.95            |

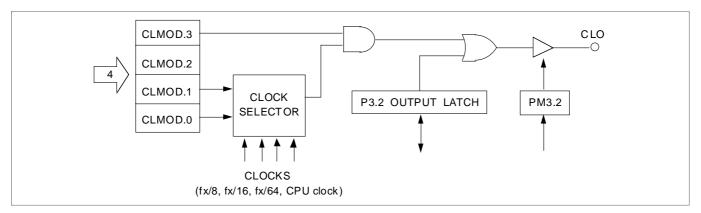

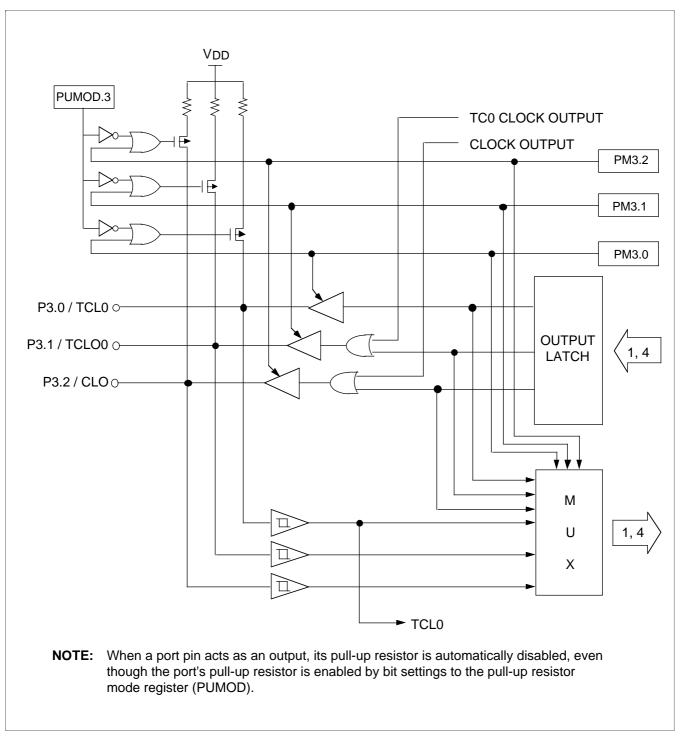

#### **CLOCK OUTPUT CIRCUIT**

The clock output circuit outputs clock pulses to the CLO pin. The clock output mode register, CLMOD, is used to enable or disable clock output to the CLO pin and to select the CPU clock source and frequency. To output a frequency, the clock output pin CLO/P3.2 must be set to output mode and the pin's latch must be cleared to "0". Bit 2 in the CLMOD register must always be "0".

Table 13. Clock Output Mode Register (CLMOD) Organization

| CLMOD Bit Settings |   | Resulting Clock Output        |                             |  |

|--------------------|---|-------------------------------|-----------------------------|--|

| CLMOD.1 CLMOD.0    |   | Clock Source                  | Frequency                   |  |

| 0                  | 0 | CPU clock (fx/4, fx/8, fx/64) | 1.05 MHz, 524 kHz, 65.5 kHz |  |

| 0                  | 1 | fx/8                          | 524 kHz                     |  |

| 1                  | 0 | fx/16                         | 262 kHz                     |  |

| 1                  | 1 | fx/64                         | 65.5 kHz                    |  |

| CLMOD.3 | Result of CLMOD.3 Setting |  |

|---------|---------------------------|--|

| 0       | Clock output is disabled  |  |

| 1       | Clock output is enabled   |  |

**NOTE**: Frequencies assume that fx = 4.19 MHz.

Figure 20. CLO Output Pin Circuit Diagram

# PROGRAMMING TIP — CPU Clock Output to the CLO Pin

To output the CPU clock to the CLO pin:

**BITS EMB** Or BITR EMB

**SMB** 15 LD EA,#40H

LD PMG1,EA P3.2 ← Output mode **BITR** P3.2 Clear P3.2 output latch

A,#9H LD LD CLMOD,A

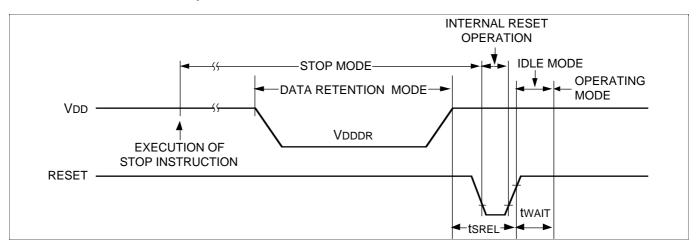

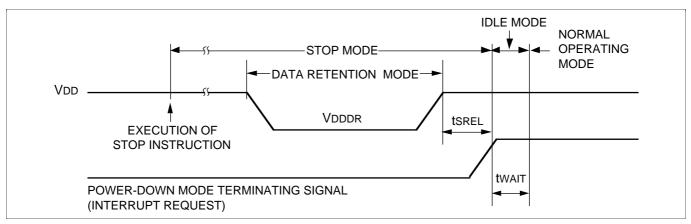

# **POWER-DOWN**

The KS57C0002/0004 microcontroller has two powerdown modes to reduce power consumption: Idle and Stop. In Idle mode, the CPU clock stops while peripherals and the oscillator continue to operate normally.

In Stop mode, system clock oscillation is halted (assuming it is currently operating), and peripheral hardware components are powered-down. The effect of Stop mode on specific peripheral hardware components — CPU, basic timer, serial I/O, timer/ counters 0, and watch timer — and on external interrupt requests, is detailed in Table 14.

**Table 14. Hardware Operation During Power-Down Modes**

| Operation                                       | Stop Mode (STOP)                                                                                  | Idle Mode (IDLE)                                                                                  |

|-------------------------------------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| Clock oscillator System clock oscillation stops |                                                                                                   | CPU clock oscillation stops (system clock oscillation continues)                                  |

| Basic timer                                     | Basic timer stops                                                                                 | Basic timer operates (with IRQB set at each reference interval)                                   |

| Serial interface                                | Operates only if external SCK input is selected as the serial I/O clock                           | Operates if a clock other than the CPU clock is selected as the serial I/O clock                  |

| Timer/counter 0                                 | Operates only if TCL0 is selected as the counter clock                                            | Timer/counter 0 operates                                                                          |

| Comparator                                      | Comparator operation is stopped                                                                   | Comparator operates                                                                               |

| Watch timer                                     | Watch timer operation is stopped                                                                  | Watch timer operates                                                                              |

| External interrupts                             | INT1 and INTK are acknowledged; INT0 is not serviced                                              | INT1 and INTK are acknowledged; INT0 is not serviced                                              |

| CPU                                             | All CPU operations are disabled                                                                   | All CPU operations are disabled                                                                   |

| Power-down mode release signal                  | Interrupt request signals (except INT0) are enabled by an interrupt enable flag or by RESET input | Interrupt request signals (except INT0) are enabled by an interrupt enable flag or by RESET input |

# **RECOMMENDED CONNECTIONS FOR UNUSED PINS**

To reduce overall power consumption, please configure unused pins according to the guidelines described in Table 15.

Table 15. Unused Pin Connections for Reduced Power Consumption

| Pin/Share Pin Names                                                                                         | Recommended Connection                                             |

|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| P0.0 / SCK<br>P0.1 / SO<br>P0.2 / SI                                                                        | Input mode: Connect to V <sub>DD</sub> Output mode: Do not connect |

| P1.0 / INT0 – P1.1 / INT1                                                                                   | Connect to V <sub>DD</sub>                                         |

| P2.0 / CIN0<br>P2.1 / CIN1<br>P2.2 / CIN2<br>P2.3 / CIN3                                                    | Connect to V <sub>DD</sub>                                         |

| P3.0 / TCLO0<br>P3.1 / TCLO1<br>P3.2 / CLO<br>P3.3 / BUZ<br>P4.0-P4.3, P5.0-P5.3<br>P6.0 / KS0 - P6.3 / BUZ | Input mode: Connect to V <sub>DD</sub> Output mode: Do not connect |

| TEST                                                                                                        | Connect to V <sub>SS</sub>                                         |

# **RESET**

Table 16 provides detailed information about hardware register values after a RESET occurs during power-down mode or during normal operation.

Table 16. Hardware Register Values After RESET

| Hardware Component or Subcomponent | If RESET Occurs During<br>Power-Down Mode                                                                          | If RESET Occurs During Normal Operation                                                                            |  |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--|

| Program counter (PC)               | Lower three bits of address 0000H are transferred to PC10–8, and the contents of 0001H to PC7–0.                   | Lower three bits of address 0000H are transferred to PC10–8, and the contents of 0001H to PC7–0.                   |  |

| Program Status Word (PSW):         |                                                                                                                    |                                                                                                                    |  |

| Carry flag (C)                     | Retained                                                                                                           | Undefined                                                                                                          |  |

| Skip flag (SC0–SC2)                | 0                                                                                                                  | 0                                                                                                                  |  |

| Interrupt status flags (IS0, IS1)  | 0                                                                                                                  | 0                                                                                                                  |  |

| Bank enable flags (EMB, ERB)       | Bit 6 of address 0000H in program memory is transferred to the ERB flag, and bit 7 of the address to the EMB flag. | Bit 6 of address 0000H in program memory is transferred to the ERB flag, and bit 7 of the address to the EMB flag. |  |

| Stack pointer (SP)                 | Undefined                                                                                                          | Undefined                                                                                                          |  |

Table 16. Hardware Register Values After RESET (Continued)

| Hardware Component or Subcomponent     | If RESET Occurs During<br>Power-Down Mode | If RESET Occurs During<br>Normal Operation |

|----------------------------------------|-------------------------------------------|--------------------------------------------|

| Data Memory (RAM):                     |                                           |                                            |

| General registers E, A, L, H, X, W, Z, | Values retained                           | Undefined                                  |

| General-purpose registers              | Values retained (Note 1)                  | Undefined                                  |

| Bank selection registers (SMB, SRB)    | 0, 0                                      | 0, 0                                       |

| BSC register (BSC0-BSC3)               | 0                                         | 0                                          |

| Clocks:                                |                                           |                                            |

| Power control register (PCON)          | 0                                         | 0                                          |

| Clock output mode register (CLMOD)     | 0                                         | 0                                          |

| Interrupts:                            |                                           |                                            |

| Interrupt request flags (IRQx)         | 0                                         | 0                                          |

| Interrupt enable flags (IEx)           | 0                                         | 0                                          |

| Interrupt priority flag (IPR)          | 0                                         | 0                                          |

| Interrupt master enable flag (IME)     | 0                                         | 0                                          |

| INT0 mode register (IMOD0)             | 0                                         | 0                                          |

| INT1 mode register (IMOD1)             | 0                                         | 0                                          |

| INTK mode register (IMODK)             | 0                                         | 0                                          |

| I/O Ports:                             |                                           |                                            |

| Output buffers                         | Off                                       | Off                                        |

| Output latches                         | 0                                         | 0                                          |

| Port mode flags (PM)                   | 0                                         | 0                                          |

| Pull-up resistor mode reg (PUMOD)      | 0                                         | 0                                          |

| Port 2 mode register (PWMOD)           | 0                                         | 0                                          |

| Basic Timer:                           |                                           |                                            |

| Count register (BCNT)                  | Undefined                                 | Undefined                                  |

| Mode register (BMOD)                   | 0                                         | 0                                          |

| Timer/Counter 0:                       |                                           |                                            |

| Count registers (TCNT0)                | 0                                         | 0                                          |

| Reference registers (TREF0)            | FFH, FFFFH                                | FFH, FFFFH                                 |

| Mode registers (TMOD0)                 | 0                                         | 0                                          |

| Output enable flags (TOE0)             | 0                                         | 0                                          |

Note1: The values of the 0F8H-0FDH are not retained when a RESET signal is input.

2–21 September 1996

Table 16. Hardware Register Values After RESET (Continued)

| Hardware Component or Subcomponent | If RESET Occurs During<br>Power-Down Mode | If RESET Occurs During<br>Normal Operation |  |  |

|------------------------------------|-------------------------------------------|--------------------------------------------|--|--|

| Watch Timer:                       |                                           |                                            |  |  |

| Watch timer mode register (WMOD)   | 0                                         | 0                                          |  |  |

| Comparator                         |                                           |                                            |  |  |

| Comparator mode register (CMOD)    | 0                                         | 0                                          |  |  |

| Comparison result register         | Undefined                                 | Undefined                                  |  |  |

| Serial I/O Interface:              |                                           |                                            |  |  |

| SIO mode register (SMOD)           | 0                                         | 0                                          |  |  |

| SIO interface buffer (SBUF)        | Values retained                           | Undefined                                  |  |  |

# I/O PORTS

The KS57C0002/0004 has two input ports and five I/O ports. There are total of 6 input pins and 18 configurable I/O pins, including 8 high-current I/O pins. This gives a total number of 24 I/O pins.

# **PORT MODE FLAGS (PM FLAGS)**

Port mode flags (PM) are used to configure I/O ports 0 and 3–6 to input or output mode. It does this by setting or clearing the corresponding I/O buffer. If a PM bit is "0", the corresponding I/O pin is set to input mode. If the PM bit is "1", the corresponding pin is set to output mode.

Table 17. Port Mode Flag Map

| PM Group ID | Address | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------|---------|-------|-------|-------|-------|

| PMG1        | FE8H    | "0"   | PM0.2 | PM0.1 | PM0.0 |

|             | FE9H    | "0"   | PM3.2 | PM3.1 | PM3.0 |

| PMG2        | FEAH    | PM4.3 | PM4.2 | PM4.1 | PM4.0 |

|             | FEBH    | "0"   | "0"   | "0"   | "0"   |

| PMG3        | FECH    | PM5.3 | PM5.2 | PM5.1 | PM5.0 |

|             | FEDH    | PM6.3 | PM6.2 | PM6.1 | PM6.0 |

# PROGRAMMING TIP — Configuring I/O Ports as Input or Output

Configure P0.0 and P3.0 as an output port and the other ports as input ports:

**BITS EMB SMB** 15 LD

EA,#11H LD PMG1,EA

LD EA,#00H

LD PMG2,EA

LD EA,#00H

LD PMG3,EA P0.0 and P3.0 ← Output

P4 ← Input

P5, P6 ← Input

# **PORT 2 MODE REGISTER (P2MOD)**

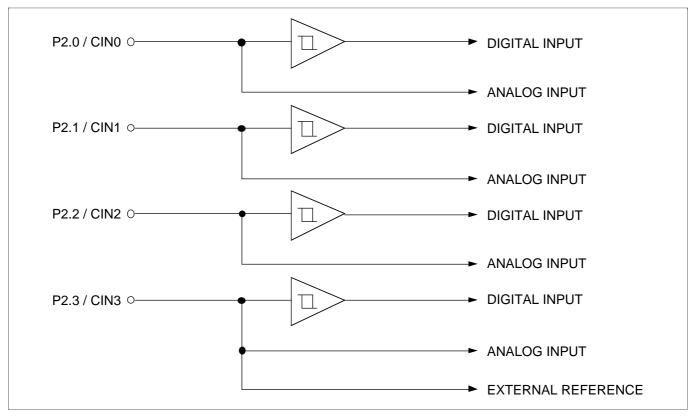

P2MOD register settings determine if port 2 is used either for analog input or for digital input.

| FE2H    |         |         | 4-Bit W |

|---------|---------|---------|---------|

| P2MOD.3 | P2MOD.2 | P2MOD.1 | P2MOD.0 |

When a P2MOD bit is set to "1", the corresponding pin is configured as a digital input pin. When set to "0", configured as an analog input pin: P2MOD.0 for P2.0, P2MOD.1 for P2.1, P2MOD.2 for P2.2, and P2MOD.3 for P2.3.

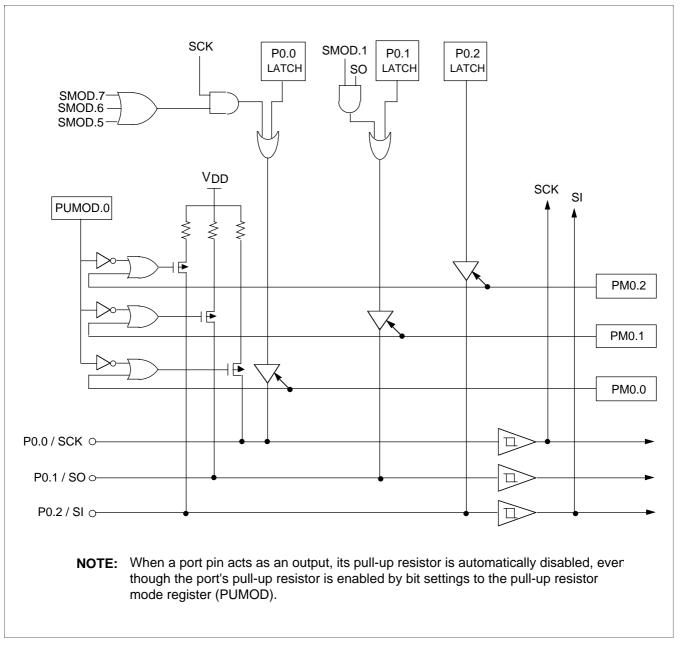

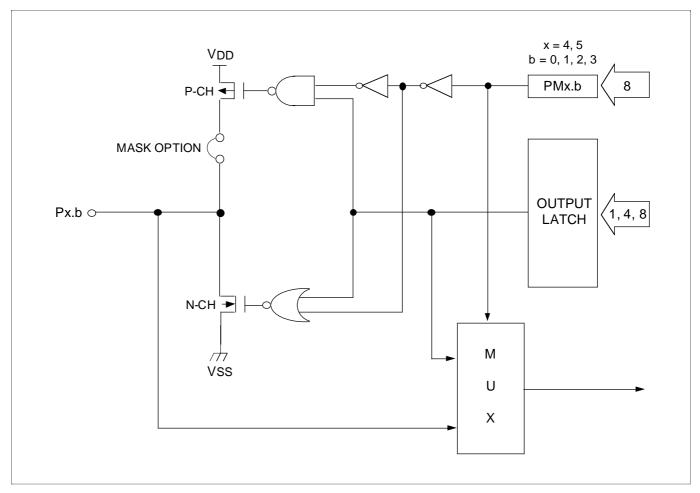

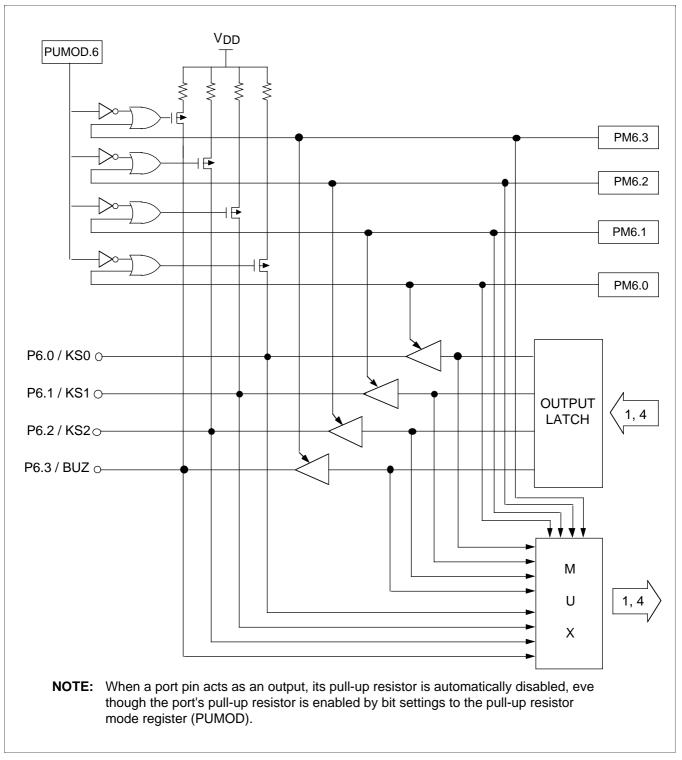

### PULL-UP RESISTOR MODE REGISTER (PUMOD)

The pull-up resistor mode register, PUMOD, is used to assign internal pull-up resistors to specific I/O ports. When a configurable I/O port pin is used as an output pin, its assigned pull-up resistor is automatically disabled, even though the pin's pull-up is enabled by a corresponding PUMOD bit setting.

When bit = "1", a pull-up resistor is assigned to the corresponding I/O port: PUMOD.3 for port 3, PUMOD.6 for port 6, and so on.

Table 18. Pull-Up Resistor Mode Register (PUMOD) Organization (8-Bit W)

| Address | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|---------|---------|---------|---------|---------|

| FDCH    | PUMOD.3 | "0"     | PUMOD.1 | PUMOD.0 |

| FDDH    | "0"     | PUMOD.6 | "0"     | "0"     |

# PROGRAMMING TIP — Enabling and Disabling I/O Port Pull-Up Resistors

P6 enable pull-up resistors, P0, P1, and P3 disable pull-up resistors.

**BITS EMB SMB** 15

LD EA.#40H

LD PUMOD, EA P6 enable

# **PORT 0 CIRCUIT DIAGRAM**

Figure 21. I/O Port 0 Circuit Diagram

# **PORT 1 CIRCUIT DIAGRAM**

Figure 22. Input Port 1 Circuit Diagram

# **PORT 2 CIRCUIT DIAGRAM**

Figure 23. Port 2 Circuit Diagram

# **PORT 3 CIRCUIT DIAGRAM**

Figure 24. Port 3 Circuit Diagram

September 1996 2–26

# **PORTS 4 AND 5 CIRCUIT DIAGRAM**

Figure 25. Circuit Diagram for Ports 4 and 5

# **PORT 6 CIRCUIT DIAGRAM**

Figure 26. Port 6 Circuit Diagram

September 1996 2–28

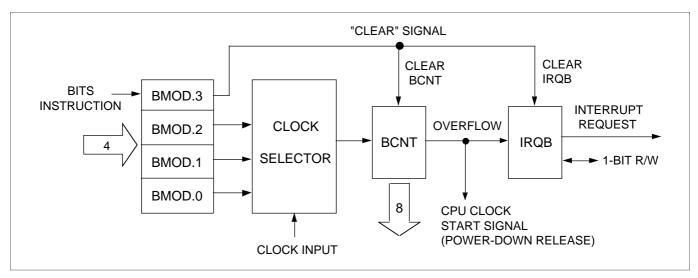

# **BASIC TIMER (BT)**

The basic timer generates interrupt requests atprecise intervals. You can use the basic timer as a "watchdog" timer for monitoring system events or use BT output to stabilize clock oscillation when Stop mode is released by an interrupt and following RESET.

#### **Interval Timer Function**

The measurement of elapsed time intervals is the basic timer's primary function. The standard interval is 256 BT clock pulses. To restart the basic timer, set bit 3 of the mode register BMOD to "1". The 8-bit counter register, BCNT, is incremented each time a clock signal is detected that corresponds to the frequency selected by BMOD. BCNT continues

incrementing as it counts BT clocks until an overflow occurs. An overflow causes the BT interrupt request flag (IRQB) to be set to "1" to signal that the designated time interval has elapsed. An interrupt request is then generated, BCNT is cleared to "0", and counting continues from 00H.

#### **Oscillation Stabilization Interval Control**

Setting bits 2–0 of the BMOD register determines the time interval (also referred to as 'wait time') required to stabilize clock signal oscillation when power-down mode is released by an interrupt. When a RESET signal is generated, the standard stabilization interval for system clock oscillation following a RESET is 31.3ms at 4.19 MHz.

Figure 27. Basic Timer Circuit Diagram

# **BASIC TIMER MODE REGISTER (BMOD)**

The basic timer mode register, BMOD, is used to select input frequency and oscillation stabilization time. The most significant bit of the BMOD register,

BMOD.3, is used to restart the basic timer. When BMOD.3 is set to "1", the contents of the BT counter register (BCNT) and the BT interrupt request flag (IRQB) are both cleared to "0", and timer operation is restarted.

Table 19. Basic Timer Mode Register (BMOD) Organization (4-Bit W)

| BMOD.3 | Basic Timer Enable/Disable Control Bit                  |

|--------|---------------------------------------------------------|

| 1      | Start basic timer; clear IRQB, BCNT, and BMOD.3 to "0". |

| BMOD.2 | BMOD.1 | BMOD.0 |

|--------|--------|--------|

| 0      | 0      | 0      |

| 0      | 1      | 1      |

| 1      | 0      | 1      |

| 1      | 1      | 1      |

| Basic Timer Input Clock       | Oscillation Stabilization     |

|-------------------------------|-------------------------------|

| fx/2 <sup>12</sup> (1.02 kHz) | 2 <sup>20</sup> /fx (250 ms)  |

| fx/2 <sup>9</sup> (8.18 kHz)  | 2 <sup>17</sup> /fx (31.3 ms) |

| fx/2 <sup>7</sup> (32.7 kHz)  | 2 <sup>15</sup> /fx (7.82 ms) |

| fx/2 <sup>5</sup> (131 kHz)   | 2 <sup>13</sup> /fx (1.95 ms) |

#### NOTES:

- 1. Clock frequencies and stabilization intervals assume a system oscillator clock frequency (fx) of 4.19 MHz.

- 2. fx = system clock frequency.

- 3. Oscillation stabilization time is the time required to stabilize clock signal oscillation after Stop mode is released.

- 4. The standard stabilization time for system clock oscillation following a RESET is 31.3 ms at 4.19 MHz.

- 5. BMOD.3 is bit addressable.

# **BASIC TIMER COUNTER (BCNT)**

BCNT is an 8-bit counter register for the basic timer. When BCNT has incremented to hexadecimal 'FFH', it is cleared to '00H' and an overflow is generated. The overflow causes the interrupt request flag, IRQB, to be set to "1". When the interrupt request is generated, BCNT immediately resumes counting incoming clock signals.

# **NOTE**

Always execute a BCNT read operation twice to eliminate the possibility of reading unstable data while the counter is incrementing. If, after two consecutive reads, the BCNT values match, you can select the latter value as valid data. Until the results of the consecutive reads match, however, the read operation must be repeated until the validation condition is met.

# PROGRAMMING TIP — Using the Basic Timer

1. To read the basic timer count register (BCNT):

|       | BITS | EMB     |

|-------|------|---------|

|       | SMB  | 15      |

| BCNTR | LD   | EA,BCNT |

|       | LD   | YZ,EA   |

|       | LD   | EA,BCNT |

|       | CPSE | EA,YZ   |

|       | JR   | BCNTR   |

2. When Stop mode is released by an interrupt, set the oscillation stabilization interval to 31.3 ms:

BITS EMB

SMB 15

LD A,#0BH

LD BMOD,A ; Wait time is 31.3 ms

STOP ; Set stop power-down mode

NOP

NOP

NOP

3. To set the basic timer interrupt interval time to 1.95 ms (at 4.19 MHz):

BITS EMB SMB 15 LD A,#0FH LD BMOD,A EI

BITS IEB ; Basic timer interrupt enable flag is set to "1"

4. Clear BCNT and the IRQB flag and restart the basic timer:

BITS EMB SMB 15 BITS BMOD.3

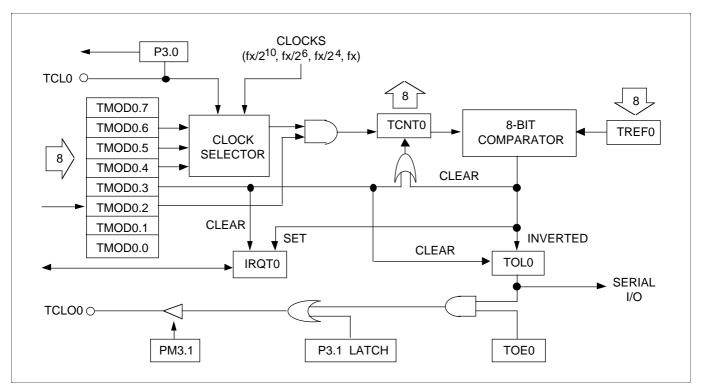

# 8-BIT TIMER/COUNTER 0 (TC0)

Timer/counter 0 (TC0) is used to count system 'events' by identifying the transition (high-to-low or low-to-high) of incoming square wave signals.

To indicate that an event has occurred, or that a specified time interval has elapsed, TC0 generates an interrupt request. By counting signal transitions and comparing the current counter value with the reference register value, TC0 can be used to measure specific time intervals.

Timer/counter 0 can supply a clock signal to the clock selector circuit of the serial I/O interface for data shifter and clock counter operations. (These internal SIO operations are controlled in turn by the SIO mode register, SMOD). This clock generation function lets you adjust data transmission rates across the serial interface.

Figure 28. TC0 Circuit Diagram

# PROGRAMMABLE TIMER/COUNTER FUNCTION

Timer/counter 0 can generate interrupt requests at various intervals, based on the selected system clock frequency. The reference register, TREF0, stores the value for the number of clock pulses to be generated between interrupt requests. The counter register, TCNT0, counts the incoming clock pulses, which are compared to the TREF0 value as TCNT0 is incremented. When TREF0 = TCNT0, the TC0 interrupt request flag (IRQT0) is set to "1", the status of TOL0 is inverted, and the interrupt is generated.

The content of TCNT0 is then cleared to 00H, and TC0 continues counting.

# **EVENT COUNTER FUNCTION**

Timer/counter 0 can be used to monitor or detect system 'events' by using the external clock input at the TCL0 pin (I/O port 3.0) as the counter source. To activate the TC0 event counter function, P3.0/TCL0 must be set to input mode. With the exception of the different TMOD0.4—TMOD0.6 settings, the operation sequence for TC's event counter function is identical to its programmable timer/counter function.

September 1996

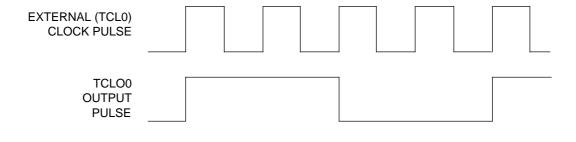

# **TC0 CLOCK FREQUENCY OUTPUT**

Using timer/counter, you can output a modifiable clock frequency to the TC0 clock output pin, TCLO0. To enable the output to the TCLO0/P3.1, the pin must be set to output mode when the timer output enable flag (TOE0) has been enabled.

# PROGRAMMING TIP — TC0 Signal Output to the TCLO0 Pin

Output a 30 ms pulse width signal to the TCLO0 pin:

**BITS EMB SMB** 15 EA,#79H LD LD TREF0,EA LD EA,#4CH LD TMOD0,EA LD EA,#20H LD PMG1,EA P3.1 ← Output mode **BITR** P3.1 P3.1 clear **BITS** TOE0

By selecting an external clock source, you can divide the incoming clock signal by the TREF0 value and then output this modified clock frequency to the TCLO0 pin.

# PROGRAMMING TIP — External TCL0 Clock Output to the TCL00 Pin

Output external TCL0 clock pulse to the TCLO0 pin (divide by four):

**BITS EMB SMB** 15 LD EA,#01H LD TREF0,EA LD EA,#0CH LD TMOD0,EA LD EA,#20H LD PMG1,EA P3.1 ← Output mode **BITR** P3.1 P3.1 clear

TOE0

**BITS**

# TC0 MODE REGISTER (TMOD0)

TMOD0 is the 8-bit mode control register for timer/counter 0. When TMOD0.3 is set to "1", the contents of TCNT0, IRQT0, and TOL0 are cleared, counting starts from 00H, and TMOD0.3 is automatically reset to "0" for normal TC0 operation. When TC0 operation stops (TMOD0.2 = "0"), the contents of the TC0 counter register, TCNT0, are retained until TC0 is re-enabled.

Table 20. TC0 Mode Register (TMOD0) Organization (8-Bit W)

| Bit Name | Setting                                               | Resulting TC0 Function                                                                                                            | Address |

|----------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------|

| TMOD0.7  | 0                                                     | MSB value always logic zero                                                                                                       |         |

| TMOD0.6  |                                                       |                                                                                                                                   | F91H    |

| TMOD0.5  | 0,1                                                   | Specify input clock edge and internal frequency                                                                                   |         |

| TMOD0.4  |                                                       |                                                                                                                                   |         |

| TMOD0.3  | 1                                                     | Clear TCNT0, IRQT0, and TOL0. Then immediately resume counting. (This bit is automatically cleared to "0" when counting resumes.) |         |

| TMOD0.2  | MOD0.2 0 Disable timer/counter; retain TCNT0 contents |                                                                                                                                   | F90H    |

|          | 1                                                     | Enable timer/counter                                                                                                              |         |

| TMOD0.1  | 0                                                     | Value always "0"                                                                                                                  |         |

| TMOD0.0  | 0                                                     | LSB value always "0"                                                                                                              |         |

Table 21. TMOD0.6, TMO0.5, and TMOD0.4 Bit Settings

| TMOD0.6 | TMOD0.5 | TMOD0.4 | Resulting Counter Source and Clock Frequency |

|---------|---------|---------|----------------------------------------------|

| 0       | 0       | 0       | External clock input (TCL0) on rising edges  |

| 0       | 0       | 1       | External clock input (TCL0) on falling edges |

| 1       | 0       | 0       | $fx/2^{10} = 4.09 \text{ kHz}$               |

| 1       | 0       | 1       | $fx/2^6 = 65.5 \text{ kHz}$                  |

| 1       | 1       | 0       | $fx/2^4 = 262 \text{ kHz}$                   |

| 1       | 1       | 1       | fx = 4.19 MHz                                |

**NOTE:** 'fx' = system clock

# PROGRAMMING TIP — Restarting TC0 Counting Operation

1. Set TC0 timer interval to 4.09 kHz:

BITS EMB

SMB 15

LD EA,#4CH

LD TMOD0,EA

EI

BITS IET0

2. Clear TCNT0, IRQT0, and TOL0. Then, restart the TC0 counting operation:

BITS EMB SMB 15 BITS TMOD0.3

# **TC0 REFERENCE REGISTER (TREF0)**

TREF0 is used to store a reference value to be compared to the incrementing TCNT0 register in order to identify an elapsed time interval.

Use the following formula to calculate the correct value to load to the TREF0 reference register:

TC0 timer interval =

(TREF0 value + 1)  $\times \frac{1}{\text{TMOD0frequencysetting}}$

(assuming a TREF0 value ≠ 0)

# TC0 OUTPUT ENABLE FLAG (TOE0)

The 1-bit timer/counter 0 output enable flag TOE0 controls output from TC0 to the TCLO0 pin.

| F92H |   |      |   | 1-Bit R/W |

|------|---|------|---|-----------|

|      | 0 | TOE0 | 0 | 0         |

When you set the TOE0 flag to "1", the contents of TOL0 can be output to the TCL00 pin.

# PROGRAMMING TIP — Setting a TC0 Timer Interval

To set a 30 ms timer interval for TC0, given fx = 4.19MHz, follow these steps.

- Select the timer/counter mode register with a maximum setup time of 62.5 ms (assume that the TC0 counter clock = fx/2<sup>10</sup>, and TREF0 is FFH):

- 2. Calculate the TREF0 value:

30 ms =

$$\frac{\text{TREF0value+1}}{4.09\text{kHz}}$$

TREF0 + 1 =  $\frac{30\text{ms}}{244\mu\text{s}}$  = 122.9 = 7AH

TREF0 value =

$$7AH - 1 = 79H$$

3. Load the value 79H to the TREF0 register:

BITS EMB

SMB 15

LD EA,#79H

LD TREF0,EA

LD EA,#4CH

LD TMOD0,EA

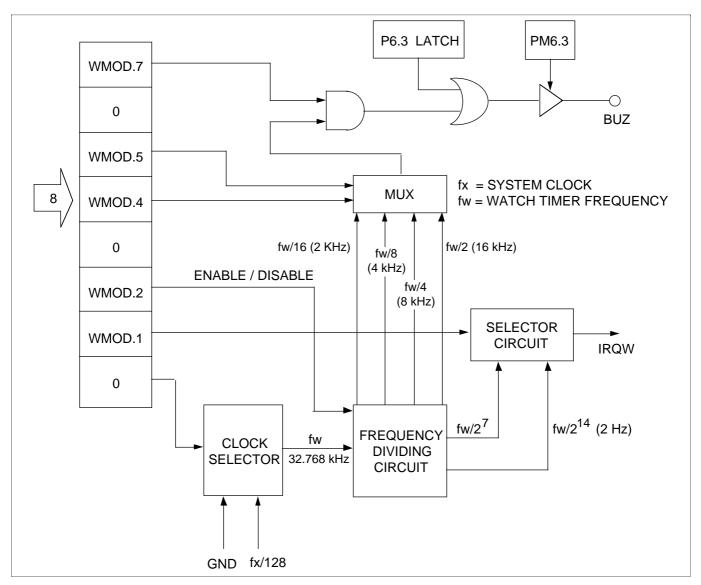

# **WATCH TIMER**

Watch timer functions include real-time and watchtime measurement and interval timing for the system clock. It is also used as a clock source for generating buzzer output.

To start the watch timer, set bit 2 of the watch timer mode register, WMOD.2, to "1". The watch timer starts, the interrupt request flag IRQW is automatically set to "1", and interrupt requests commence in 0.5-second intervals. Because the watch timer functions as a quasi-interrupt instead of a vectored interrupt, the IRQW flag should be cleared to "0" by program

software as soon as a requested interrupt service routine has been executed.

The watch timer can generate a steady 2 kHz, 4 kHz, 8 kHz, or 16 kHz signal to the BUZ pin. To generate a BUZ signal, clear the output latch for I/O port 6.3 to "0" and set the port 6.3 output mode flag (PM6.3) to output mode.

By setting WMOD.1 to "1", the watch timer functions in high-speed mode, generating an interrupt every 3.91 ms. High-speed mode is useful for timing events during program debugging sequences.

Figure 29. Watch Timer Circuit Diagram

September 1996 2–36

# **WATCH TIMER MODE REGISTER (WMOD)**

The watch timer mode register WMOD is used to select specific watch timer operations.

Table 22. Watch Timer Mode Register (WMOD) Organization (8-Bit W)

| Bit Name   | Val | ues |                                                        |      |  |  |

|------------|-----|-----|--------------------------------------------------------|------|--|--|

| WMOD.7 0   |     |     | Disable buzzer (BUZ) signal output                     |      |  |  |

|            | 1   | 1   | Enable buzzer (BUZ) signal output                      |      |  |  |

| WMOD.6     | "(  | )"  | Always "0"                                             |      |  |  |

| WMOD.54    | 0   | 0   | 2 kHz buzzer (BUZ) signal output                       | F89H |  |  |

|            | 0   | 1   | 4 kHz buzzer (BUZ) signal output                       |      |  |  |

|            | 1   | 0   | 8 kHz buzzer (BUZ) signal output                       |      |  |  |

|            | 1   | 1   | 16 kHz buzzer (BUZ) signal output                      |      |  |  |

| WMOD.3     | "(  | )"  | Always "0"                                             |      |  |  |

| WMOD.2     | (   | )   | Disable watch timer; clear frequency dividing circuits |      |  |  |

| 1          |     | 1   | Enable watch timer                                     | F88H |  |  |

| WMOD.1 0 1 |     | )   | Normal mode; sets IRQW to 0.5 s                        |      |  |  |

|            |     | 1   | High-speed mode; sets IRQW to 3.91 ms                  |      |  |  |

| WMOD.0     | (   | )   | Always "0"                                             |      |  |  |

NOTE: System clock frequency (fx) is assumed to be 4.19 MHz.

# PROGRAMMING TIP — Using the Watch Timer

1. Select a 0.5 second interrupt, and 2 kHz buzzer enable:

BITS EMB SMB 15 LD EA,#80H LD PMG3,EA

LD PMG3,EA ; P6.3  $\leftarrow$  Output mode BITR P6.3 ; Clear P6.3 output latch LD EA.#84H

LD EA,#84H LD WMOD,EA BITS IEW

2. Sample real-time clock processing method:

CLOCK BTSTZ IRQW ; 0.5 second check

RET : No, return

Yes, 0.5 second interrupt generation

Increment HOUR, MINUTE, SECOND

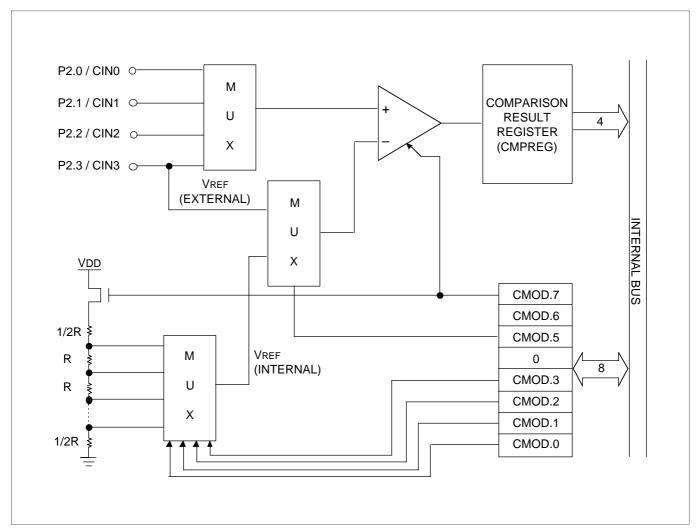

## **COMPARATOR**

Port 2 can be used as a analog input port for the 4channel comparator block. The reference voltage for the comparator can be supplied either internally or externally at P2.3.

When internal reference voltage is used, four channels (P2.0–P2.3) are used for analog inputs and the internal reference voltage is varies at 16 levels. If

an external reference voltage is input at P2.3, the other three pins (P2.0–P2.2) in port 2 are used for analog input. Unused port 2 pins must be connected to  $V_{DD}$ .

When a conversion is completed, the result is saved in the comparison result register CMPREG. The initial values of the CMPREG are undefined and the comparator operation is disabled by a RESET.

Figure 30 Comparator Circuit Diagram

September 1996 2–38

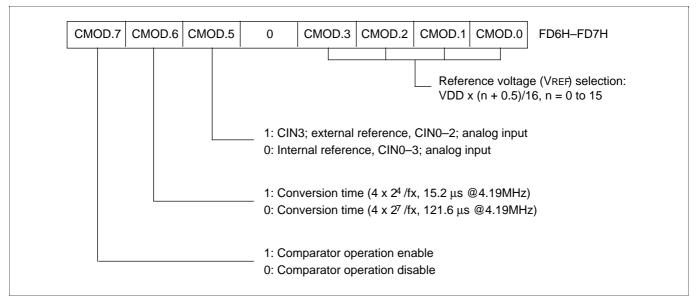

## **COMPARATOR MODE REGISTER (CMOD)**

The comparator mode register (CMOD) is used to set the operation mode of the comparator. Based on the CMOD.5 bit setting, an internal or an external reference voltage is input for the comparator, as follows:

#### When CMOD.5 is "0":

- A reference voltage is selected by the CMOD.0 to CMOD.3 bit settings.

- P2.0 to P2.3 are used as analog input pins.

- The internal digital-to-analog converter generates 16 reference voltages.

- The comparator can detect a 150 mV difference between the reference voltage and analog input voltages.

- Comparator results are written into 4-bit comparison result register (CMPREG).

When CMOD.5 is set to "1":

- External reference voltage is supplied from P2.3/CIN3.

- P2.0 to P2.2 are used as the analog input pins.

- The comparator can detect a 150 mV difference between the reference voltage and analog input voltages.

- Bits 0–2 in the CMPREG register contain the results (the content of bit 3 is not used).

Bit 6 in the CMOD register controls conversion time while bit 7 enables or disables comparator operation to reduce power consumption.

Figure 31. Comparator Mode Register Organization

## **PORT 2 MODE REGISTER (P2MOD)**

P2MOD register settings determine if port 2 is used for analog or digital input.

| FE2H    |         |         | 4-Bit W |

|---------|---------|---------|---------|

| P2MOD.3 | P2MOD.2 | P2MOD.1 | P2MOD.0 |

When a P2MOD bit is set to "1", the corresponding pin is configured as a digital input pin. When it is "0", the corresponding pin is configured as an analog input: P2MOD.0 for P2.0, P2MOD.1 for P2.1, P2MOD.2 for P2.2, and P2MOD.3 for P2.3.

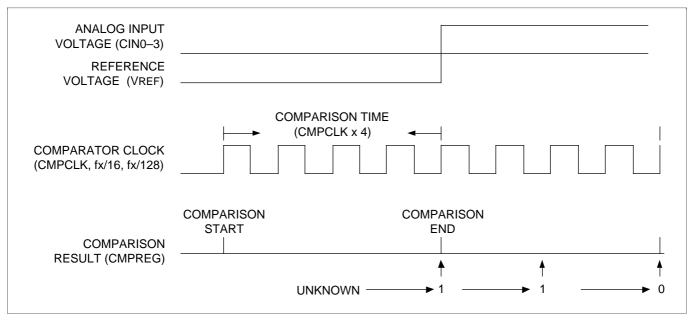

## **COMPARATOR OPERATION**

The comparator compares analog voltage input at CIN0–CIN3 with an external or internal reference voltage (V<sub>REF</sub>) that is selected by CMOD register. The result is written to the comparison result register CMPREG at address FD4H.

The comparison result is calculated as follows:

If "1" Analog input voltage ≥ V<sub>REF</sub> + 150 mV

If "0" Analog input voltage  $\leq V_{REF} - 150 \text{ mV}$

To obtain a comparison result, the data must be read out from the CMPREG register after V<sub>REF</sub> is updated by changing the CMOD value after a conversion time has elapsed.

Figure 32. Conversion Characteristics

# PROGRAMMING TIP — Programming the Comparator

The following program example converts the analog voltage input at CIN0-CIN2 pins into 4-bit digital code.

BITR EMB LD A,#0H

LD P2MOD,A ; Analog input selection (CIN0–CIN3) LD EA,#8XH ; x = 0-F, comparator enable

; Internal reference, conversion time (121.6  $\mu$ s)

LD CMOD,EA WAIT LD A,#0H

INCS A JR WAIT

LD A,CMPREG ; Read the result

LD P4,A ; Output the result from port 4

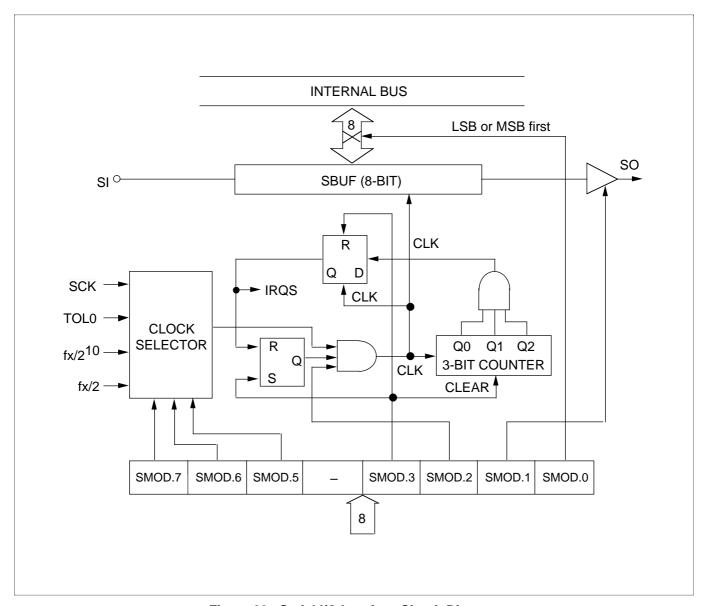

## **SERIAL I/O INTERFACE**

Using the serial I/O interface, you can exchange 8-bit data with an external device. The serial interface can run off an internal or an external clock source, or the TOL0 signal that is generated by the 8-bit timer/counter 0, TC0. If you use the TOL0 clock signal, you can modify its frequency to adjust the serial data transmission rate.

Figure 33. Serial I/O Interface Circuit Diagram

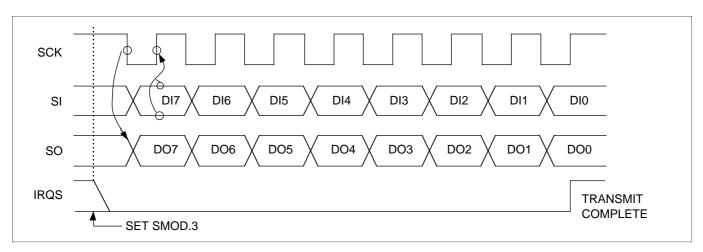

## **SERIAL I/O MODE REGISTER (SMOD)**

The serial I/O mode register (SMOD) specifies the operation mode of the serial interface. SMOD register settings enable you to select either MSB-first or LSB-first serial transmission, and to operate in transmitand-receive mode or receive-only mode. When SMOD.3 is set to "1", the contents of the serial interface interrupt request flag, IRQS, and the 3-bit serial clock counter are cleared, and SIO operations are initiated. When the SIO transmission starts, SMOD.3 is cleared to "0".

## **SERIAL I/O BUFFER REGISTER (SBUF)**

When the serial interface operates in transmit-and-receive mode (SMOD.1 = "1"), transmit data in the SIO buffer register are output to the SO pin at the rate of one bit for each falling edge of the SIO clock. Receive data is simultaneously input from the SI pin to SBUF at the rate of one bit for each rising edge of the SIO clock.

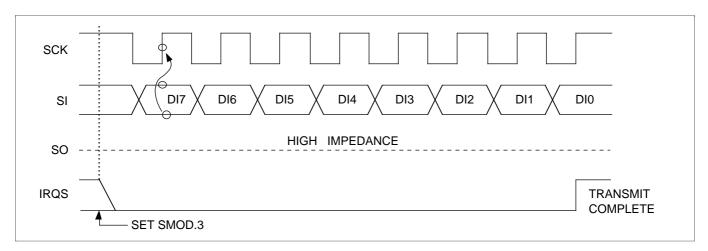

When receive-only mode is used, incoming data is input to the SIO buffer at the rate of one bit for each rising edge of the SIO clock. SBUF can be read or written using 8-bit RAM control instructions.

Table 23. SIO Mode Register (SMOD) Organization (8-Bit W)

| SMOD.0 | 0 | Most significant bit (MSB) is transmitted first                                                                                         |

|--------|---|-----------------------------------------------------------------------------------------------------------------------------------------|

|        | 1 | Least significant bit (LSB) is transmitted first                                                                                        |

| SMOD.1 | 0 | Receive-only mode; output buffer is off                                                                                                 |

|        | 1 | Transmit-and-receive mode                                                                                                               |

| SMOD.2 | 0 | Disable the data shifter and clock counter; retain contents of IRQS flag when serial transmission is halted                             |

|        | 1 | Enable the data shifter and clock counter; set IRQS flag to "1" when serial transmission is halted                                      |

| SMOD.3 | 1 | Clear IRQS flag and 3-bit clock counter to "0"; initiate transmission and then reset this bit to "0"; this bit is also bit-addressable. |

| SMOD.4 | 0 | Bit not used; value is always "0"                                                                                                       |

| SMOD.7 | SMOD.6 | SMOD.5 | Clock Selection                    | R/W Status of SBUF                                                  |

|--------|--------|--------|------------------------------------|---------------------------------------------------------------------|

| 0      | 0      | 0      | External clock at SCK pin          | SBUF is enabled when SIO operation is halted or when SCK goes high. |

| 0      | 0      | 1      | Use TOL0 clock from TC0            |                                                                     |

| 0      | 1      | х      | CPU clock: fx/4, fx/8, fx/64       | Enable SBUF read/write                                              |

| 1      | 0      | 0      | 4.09 kHz clock: fx/2 <sup>10</sup> | SBUF is enabled when SIO operation is halted or when SCK goes high. |

| 1      | 1      | 1      | 262 kHz clock: fx/2 <sup>4</sup>   |                                                                     |

#### NOTES:

- 1. 'fx' = system clock; 'x' means 'don't care.'

- 2. kHz frequency ratings assume a system clock (fx) running at 4.19 MHz.

- 3. The SIO clock selector circuit cannot select a fx/2<sup>4</sup> clock if the CPU clock is fx/64.

Figure 34. SIO Timing in Transmit/Receive Mode

Figure 35. SIO Timing in Receive-Only Mode

# PROGRAMMING TIP — Setting Transmit/Receive Modes for Serial I/O

Transmit the data value 48H through the serial I/O interface using an internal clock frequency of fx/2<sup>4</sup> and in MSB-first mode:

> **BITS EMB** SMB 15 EA,#03H LD LD PMG1,EA P0.0 / SCK and  $P0.1 / SO \leftarrow Output$ EA,#48H LD LD SBUF, EA LD EA,#0EEH LD SMOD, EA SIO data transfer

PROGRAMMING TIP — Setting Transmit/Receive Modes for Serial I/O (Continued)

2. Use CPU clock to transfer and receive serial data at high speed:

**BITR EMB** EA,#03H LD LD P0.0 / SCK and  $P0.1 / SO \leftarrow Output$ ,  $P0.2 / SI \leftarrow Input$ PMG1,EA LD EA,TDATA TDATA address = Bank0(20H-7FH) LD SBUF,EA LD EA,#4FH SMOD, EA LD SIO start **BITR** SIO Interrupt Enable **IES STEST BTSTZ IRQS** JR STEST LD EA,SBUF LD RDATA,EA ; RDATA address = Bank0 (20H-7FH)

# PROGRAMMING TIP — Setting Transmit/Receive Modes for Serial I/O (Continued)

3. Transmit and receive an internal clock frequency of 4.09 kHz (at 4.19 MHz) in LSB-first mode: